UART串口通信-基于FIFO

说明:

- 本文档由DuRuofu撰写,由DuRuofu负责解释及执行。

- 本文记录使用FPGA实现简单UART串口通信-基于FIFO

修订历史:

| 文档名称 | 版本 | 作者 | 时间 | 备注 |

|---|---|---|---|---|

| UART串口通信-基于FIFO | v1.0.0 | DuRuofu | 2024-01-28 | 首次建立 |

UART串口通信-基于FIFO

代码:https://github.com/DuRuofu/FPGA_Learning/tree/master/06_uart_fifo

目标

实现收发双缓冲的串口回环实验

一、整体框图

顶层模块:

子模块模块:

整体框图:

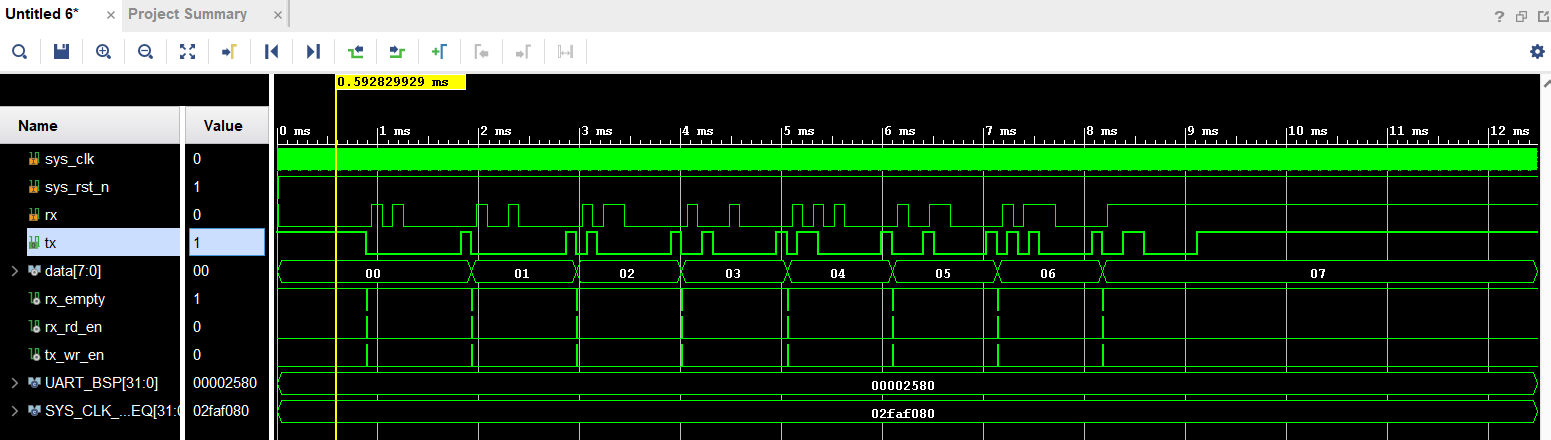

二、模块波形图

以9600波特率为例。

接收模块:

发送模块:

三、代码编写

3.1 串口接收模块

模块代码:

1 | |

模块测试:

1 | |

3.2 串口发送模块

模块代码:

1 | |

仿真代码

1 | |

3.3 串口接收缓冲

1 | |

3.3 串口发送缓冲

1 | |

3.3 串口顶层模块

模块代码:

1 | |

仿真代码:

1 | |

仿真效果(顶层模块):

四、实际测试效果

参考链接

- https://search.bilibili.com/all?vt=76757802&keyword=%E6%AD%A3%E7%82%B9%E5%8E%9F%E5%AD%90fpga&from_source=webtop_search&spm_id_from=333.1007&search_source=5

- https://www.bilibili.com/video/BV1y34y147s5/?spm_id_from=333.337.top_right_bar_window_history.content.click&vd_source=ef5a0ab0106372751602034cdd9ab98e

- https://blog.csdn.net/wanerXR/article/details/125120315

- https://www.cnblogs.com/lzbmeee/p/17624957.html

- https://www.bilibili.com/video/BV1N5411v7GN/?spm_id_from=333.1007.top_right_bar_window_history.content.click&vd_source=ef5a0ab0106372751602034cdd9ab98e

UART串口通信-基于FIFO

https://www.duruofu.xyz/posts/60775/